# **Solutions - Midterm Exam**

(February 18th @ 5:30 pm)

Presentation and clarity are very important! Show your procedure!

## **PROBLEM 1 (20 PTS)**

a) Complete the following table. The decimal numbers are unsigned: (6 pts.)

| Decimal | BCD          | Binary   | Reflective Gray Code |

|---------|--------------|----------|----------------------|

| 97      | 10010111     | 1100001  | 1010001              |

| 51      | 01010001     | 110011   | 101010               |

| 98      | 10011000     | 1100010  | 1010011              |

| 156     | 000101010110 | 10011100 | 11010010             |

b) Complete the following table. Use the fewest number of bits in each case: (12 pts.)

| REPRESENTATION |                    |                |                |  |

|----------------|--------------------|----------------|----------------|--|

| Decimal        | Sign-and-magnitude | 1's complement | 2's complement |  |

| -32            | 1100000            | 1011111        | 100000         |  |

| -76            | 11001100           | 10110011       | 10110100       |  |

| -33            | 1100001            | 1011110        | 1011111        |  |

| 69             | 01000101           | 01000101       | 01000101       |  |

| -64            | 11000000           | 10111111       | 1000000        |  |

| -19            | 110011             | 101100         | 101101         |  |

c) Convert the following decimal numbers to their 2's complement representations. (2 pts)

```

7 -31.3125

+31.3125 = 011111.0101 \checkmark +17.375 = 010001.011 \Rightarrow 100000.1011

```

### PROBLEM 2 (10 PTS)

0x200000 to 0x3FFFFF

- The figure below depicts the entire memory space of a microprocessor. Each memory address occupies one byte.  $1KB = 2^{10}$  bytes,  $1MB = 2^{20}$  bytes,  $1GB = 2^{30}$  bytes

- ✓ What is the size (in bytes, KB, or MB) of the memory space? What is the address bus size of the microprocessor?

Address space:  $0 \times 000000$  to  $0 \times FFFFFFF$ . To represents all these addresses, we require 24 bits. So, the address bus size of the microprocessor is 24 bits. The size of the memory space is  $2^{24} = 16 \text{ MB}$

- ✓ If we have a memory chip of 2 MB, how many bits do we require to address those 2 MB of memory?

- $2 \text{ MB} = 2^{21} \text{ bytes. Thus, we require } 21 \text{ bits to address the memory device.}$

- ✓ We want to connect the 2 MB memory chip to the microprocessor. The figure shows all the occupied portions of the memory space. Provide an address range so that 2 MB of memory is properly addressed. You can only use the non-occupied portions of the memory space as shown in the figure below.

2 MB of memory require 21 bits. The 21-bit address range would be from  $0 \times 000000$  to  $0 \times 1$  FFFFF. Within the entire 24-bit memory space. Any 24-bit range, where the 21 LSBs go from  $0 \times 000000$  to  $0 \times 1$  FFFFF, would be valid: this results in 8 valid ranges. However, there are occupied portions in the figure, leaving only four possible ranges:

• 0x400000 to  $0x5FFFFFF \rightarrow$  we pick this one!

1

Instructor: Daniel Llamocca

#### PROBLEM 3 (12 PTS)

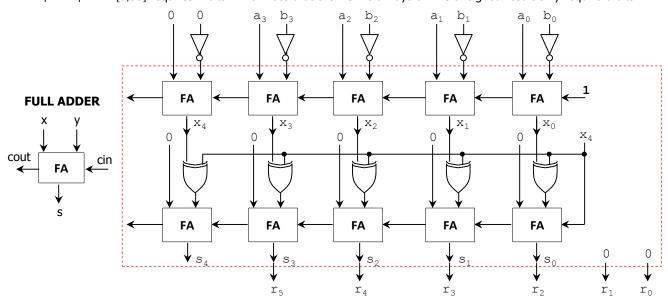

• Given two 4-bit <u>unsigned</u> numbers A, B, sketch the circuit that computes  $|A - B| \times 4$ . For example:  $A = 0011, B = 1010 \rightarrow |A - B| = 7$ ,  $|A - B| \times 4 = 28$ . You can only use full adders and logic gates. Make sure your circuit avoids overflow.

$A = a_3 a_2 a_1 a_0$ ,  $B = b_3 b_2 b_1 b_0$

$A, B \in [0,15] \to A, B$  require 4 bits in unsigned representation. However, to get the proper result of A - B, we need to use the 2C representation, where A, B require 5 bits in 2C.

- $\checkmark$   $X = A B \in [-15,15]$  requires 5 bits in 2C. Thus, we need to zero-extend A and B to convert them to 2C representation.

- $\checkmark$   $|X| = |A B| \in [0.15]$  requires 5 bits in 2C. Thus, the second operation  $0 \pm X$  only requires 5 bits.

- $If x_4 = 0 \rightarrow X \ge 0 \rightarrow \text{we do } 0 + X.$

- $\checkmark$   $R = |A B| \times 4 \in [0,60]$  requires 7 bits in 2C. Note that the MSB is always 0. The unsigned result only require 6 bits.

#### **PROBLEM 4 (18 PTS)**

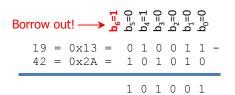

a) Perform the following additions and subtractions of the following unsigned integers. Use the fewest number of bits n to represent both operators. Indicate every carry (or borrow) from c₀ to cₙ (or b₀ to bₙ). For the addition, determine whether there is an overflow. For the subtraction, determine whether we need to keep borrowing from a higher byte. (6 pts)

✓ 51 + 27

b) Perform the following operations, where numbers are represented in 2's complement. Indicate every carry from c<sub>0</sub> to c<sub>n</sub>. For each case, use the fewest number of bits to represent the summands and the result so that overflow is avoided. (8 pts)

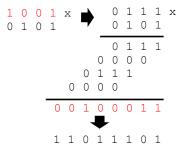

c) Get the multiplication result of the following numbers that are represented in 2's complement arithmetic with 4 bits. (4 pts)  $\sqrt{-7} \times 5$ .

## PROBLEM 5 (10 PTS)

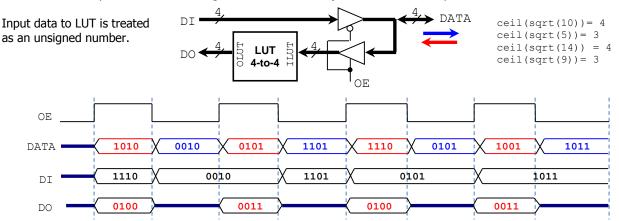

• Given the following circuit, complete the timing diagram (signals DO and DATA). The LUT 4-to-4 implements the following function: OLUT = [sqrt(ILUT)]. For example:  $ILUT = 1100 \rightarrow OLUT = 0100$

## **PROBLEM 6 (15 PTS)**

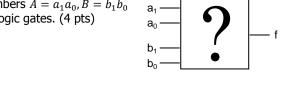

a) We want to design a circuit that determines whether two 2-bit numbers  $A=a_1a_0, B=b_1b_0$  are equal: f=1 if A=B, f=0 if  $A\neq B$ . Sketch this circuit using logic gates. (4 pts)

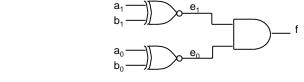

b) Implement the previous circuit using ONLY 2-to-1 MUXs (AND, OR, NOT, XOR gates are not allowed). (11 pts)

$$f(a_{1},b_{1},a_{0},b_{0}) = (\overline{a_{1}}\oplus b_{1})(\overline{a_{0}}\oplus b_{0})$$

$$f = \overline{a_{1}}f(0,b_{1},a_{0},b_{0}) + a_{1}f(1,b_{1},a_{0},b_{0}) = \overline{a_{1}}\left(\overline{b_{1}}(\overline{a_{0}}\oplus \overline{b_{0}})\right) + a_{1}\left(b_{1}(\overline{a_{0}}\oplus \overline{b_{0}})\right) = \overline{a_{1}}g(b_{1},a_{0},b_{0}) + a_{1}h(b_{1},a_{0},b_{0})$$

$$g(b_{1},a_{0},b_{0}) = \overline{b_{1}}(\overline{a_{0}}\oplus b_{0}) + b_{1}(0)$$

$$h(b_{1},a_{0},b_{0}) = \overline{b_{1}}(0) + b_{1}(\overline{a_{0}}\oplus b_{0})$$

$$t(a_{0},b_{0}) = (\overline{a_{0}}\oplus b_{0}) = \overline{a_{0}}(\overline{b_{0}}) + a_{0}(b_{0})$$

$$Also: \overline{b_{0}} = \overline{b_{0}}(1) + b_{0}(0)$$

$$b_{0}$$

$$a_{0}$$

$$b_{1}$$

$$a_{1}$$

3

#### PROBLEM 7 (15 PTS)

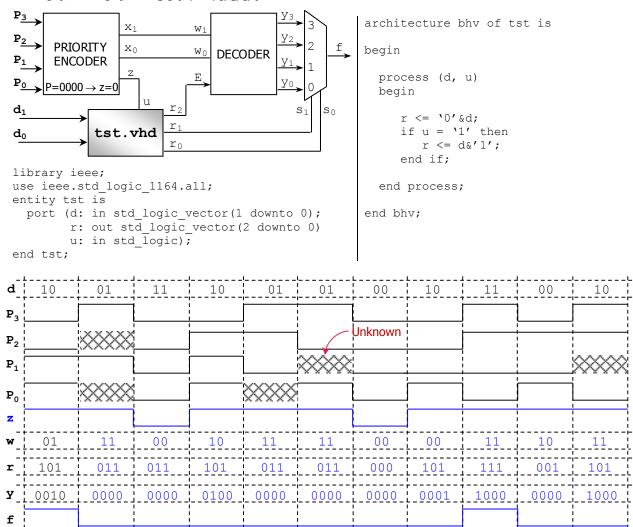

• Complete the timing diagram of the following circuit. The VHDL code (tst.vhd) corresponds to the shaded circuit.  $d = d_1 d_0$ ,  $w = w_1 w_0$ ,  $r = r_2 r_1 r_0$ ,  $y = y_3 y_2 y_1 y_0$

4